#### DOCTORAL THESIS

# Manycore Architectures and SIMD Optimizations for High Performance Computing

Marcos Horro Varela 2022

# Manycore Architectures and SIMD Optimizations for High Performance Computing

Marcos Horro Varela

Doctoral Thesis

April 2022

PhD Advisors:

Gabriel Rodríguez Álvarez

Juan Touriño Domínguez

PhD Program in Information Technology Research

Dr. Gabriel Rodríguez Álvarez Profesor Titular de Universidad Dpto. de Ingeniería de Computadores Universidade da Coruña

Dr. Juan Touriño Domínguez

Catedrático de Universidad

Dpto. de Ingeniería de

Computadores

Universidade da Coruña

#### **CERTIFICAN**

Que la memoria titulada "Manycore Architectures and SIMD Optimizations for High Performance Computing" constituye un trabajo original de investigación realizado por D. Marcos Horro Varela bajo nuestra dirección en el marco del Programa de Doctorado en Investigación en Tecnologías de la Información de la Universidade da Coruña, y concluye la Tesis Doctoral que presenta para optar al grado de Doctor con la Mención de Doctor Internacional.

En A Coruña, a 1 de marzo de 2022

Fdo.: Gabriel Rodríguez Álvarez Fdo.: Juan Touriño Domínguez Director de la Tesis Doctoral Director de la Tesis Doctoral

Fdo.: Marcos Horro Varela Autor de la Tesis Doctoral

## **Agradecementos**

Non é doado condensar nun par de liñas todas as sensacións e sentimentos atopados despois dun arduo traballo de máis de catro anos, cunha pandemia mundial de por medio. A investigación é, en moitas ocasións, un traballo individual, solitario e frustrante, pero tamén curioso, interesante, satisfactorio, enriquecedor e que pode ser compartido con milleiros de persoas en todo o mundo, non só no ámbito científico. Experimentei todas as facianas emocionais nesta travesía, pero agora só podo ter palabras de agradecemento a todas as persoas e institucións que apoiaron este traballo e me permitiron completar esta Tese de forma satisfactoria.

Tiven a sorte de que Gabriel e Juan contactaran comigo en setembro do 2014. Primeiro para completar o traballo de fin de grao, despois o do mestrado, e así continuar ca Tese Doutoral. Agradecerlles infinitamente a súa confianza durante estes anos, polos momentos nos que os resultados non acompañaban, e por todas as facilidades laborais e académicas que me permitiron investigar aquelas materias do meu interese. En especial a Gabriel, por ser o meu salvavidas tanto no persoal como no laboral, gracias de verdade. Do mesmo xeito, agradecer a todos os meus compañeiros dos laboratorios 0.2 e 1.2, con especial mención por estes anos a Toño, Christian, Diego, Sergio, Santa Comba, Róber, Deibe, Ana, Pérez, Andión, Jorge, e Nuria; sen vós o camiño sería aínda máis pesado. Tamén aos meus compañeiros e amigos de grao e mestrado na Coruña, con mención a Feal, Rubén, Fran, Avelino e Eloy. Estender o meu agradecemento e apoio institucional a todos os profesores

e membros do Grupo de Arquitectura de Computadores, ao Departamento de Enxeñaría de Computadores, á Facultade de Informática da Coruña e á Universidade da Coruña. Simplemente grazas.

Gustaríame agradecer ao meu ex-profesor J. B. Búa por despertar a miña curiosidade en canto ás matemáticas e á investigación cando aínda cursaba  $3^{\circ}$  da ESO.

The same way, I gratefully thank Dr. Louis-Noël Pouchet for hosting me and advising me in one of my best experiences working abroad at the Colorado State University, Fort Collins. It has been an honor working those three months with you, and extending our collaborations further, *merci beaucoup*. Also thanks to my *mecedoras* Lucía and Hassna for making my stay great in Fort Collins.

Agradecementos tamén ao resto de entidades financeiras deste traballo: ás redes estatais de investigación, ás redes europeas, á Xunta de Galicia, e ao Goberno de España. Tamén agradecementos á empresa Inditex S.A. polo financiamento da estadía nos EUA.

Se cheguei ata aquí é por meus pais, os meus piares vitais: nunca terei palabras suficientes para agradecer o voso sacrificio por darme a mellor educación e por darme todos os medios posibles para chegar a ser a persoa que son hoxe en día, gracias infinitas. Gracias tamén ao meu irmán Jorge polo seu apoio incondicional, e a toda a miña familia por crer en min. Gracias tamén á miña outra familia: gracias aos meus amigos de Cambados por estar sempre aí, por facer que calquera sitio sexa como estar na casa, con mención a Me, Clara, Emm, Xabi, Martin, Deivid, Johnny, Agarunde, Piñe, Duri, Angelote e Vítor. Gracias aos meus amigos de Coruña, con especial mención a Domingo, aos meus Javis e a Miwel.

A Marta, porque sen ti o que vén despois disto deixa de ter sentido, a ti por ser o meu remanso nesta viaxe tan movida.

Non caben nestas liñas todas as palabras de agradecemento. Moitas gracias de todo corazón.

A Coruña

Markos Horro

"La ciencia es un mito, sólo que es el mito más hermoso, el único generalizable a toda la especie y quizás el más digno de respetarse." —Antonio Escohotado

> "En tanto en cuanto nos 'dean' lo que es nuestro, discutiremos ese 'conceto' con el fin de discutirlo." —M. Manquiña

#### Resumo

Nos últimos cincuenta anos a arquitectura de computadores estivo marcada pola capacidade de aumentar o número de transistores nos microchips segundo a Lei de Moore. Esta corrente cambiou drasticamente na última década. O paralelismo xoga un factor clave nos deseños modernos: dende un punto de vista hardware aumentando o número de CPUs, e dende unha perspectiva software explotando as capacidades arquitectónicas con especial énfase nas unidades vectoriais. Nesta Tese poñemos o foco en dúas dimensións ortogonais: a análise e optimización do tráfico de coherencia en arquitecturas manycore, e o desenvolvemento de optimizacións vectoriais. Na primeira dimensión desenvolvemos técnicas estáticas e dinámicas para mellorar a afinidade entre as CPUs e os datos naquelas arquitecturas que implementan redes de interconexión en malla. A nosa proposta reduce a contención nesas mallas mellorando a localidade dos datos de acordo á distribución física dos compoñentes. Na segunda dimensión desenvolvemos un compilador fonte-a-fonte para vectorizar códigos con patróns de acceso a memoria irregulares. Presentamos dúas contribucións: estratexias para recuperar de forma vectorial direccións de memoria non contiguas, e a fusión de reducións independentes. Desenvolvemos un sistema SMT para a xeración de alternativas de empaquetado de operandos aleatorios baseadas no conxunto de instrucións da arquitectura subxacente, e unha ferramenta para a caracterización de arquitecturas. A nosa avaliación mostra potenciais beneficios nestes códigos irregulares aplicando as nosas propostas.

#### Resumen

En los últimos cincuenta años la arquitectura de computadores estuvo condicionada por la capacidad de aumentar el número de transistores en los microchips siguiendo la Ley de More. Esta tendencia cambió drásticamente en la última década. El paralelismo es ahora un factor clave en los diseños modernos: desde una perspectiva hardware aumentando el número de CPUs, y desde un punto de vista software explotando las capacidades arquitecturales con especial énfasis en las unidades vectoriales. En esta Tesis ponemos el foco en dos dimensiones ortogonales: el análisis y optimización del tráfico de coherencia caché en arquitecturas manycore, y el desarrollo de optimizaciones vectoriales. Para la primera dimensión hemos desarrollado técnicas estáticas y dinámicas para mejorar la afinidad entre las CPUs y los datos en arquitecturas con redes de interconexión en malla. Nuestra propuesta reduce la contención en las mallas mejorando la localidad de los datos siguiendo la distribución física de los componentes. En la segunda dimensión hemos desarrollado un compilador fuente-a-fuente para vectorizar códigos con patrones de acceso a memoria irregulares. Presentamos dos contribuciones: estrategias para recuperar de forma vectorial direcciones de memoria no contiguas, y la fusión de reducciones independientes. Hemos desarrollado un sistema SMT para la generación de alternativas de empaquetamiento de operandos aleatorios basadas en el conjunto de instrucciones de la arquitectura subyacente, y una herramienta para la caracterización de arquitecturas. Nuestra evaluación muestra potenciales beneficios en estos códigos irregulares aplicando nuestras propuestas.

### **Abstract**

For the past fifty years computer architecture has been driven by the ability to etch more transistors onto a single die following the Moore's Law. This trend changed in the past decade. Parallelism is now a key factor in modern designs: from the hardware side by scaling the number of cores, and from the software side by exploiting the capabilities available in the architecture, emphasizing on the SIMD units. In this Thesis we focus on two orthogonal dimensions: the analysis and optimization of coherence traffic in modern manycores, and the development of SIMD optimizations. For the first dimension we develop static and dynamic techniques for enhancing core-to-data affinity for manycores featuring mesh interconnection networks. Our approach reduces the contention on these meshes by improving data locality according to the physical layout. For the second dimension we develop a source-to-source compiler for vectorizing codes presenting irregular access patterns. We present two main contributions: strategies for gathering non-contiguous memory addresses, and fusing independent reductions. We have developed an SMT-based system to generate alternatives for packing random operands from memory based on the host ISA, and a profiling framework for characterizing platforms. Our evaluation shows promising speedups when applying these SIMD optimizations to those codes.

### **Preface**

Parallelism has become more important in hardware development as the frequency increase has reached its physical limit due to the power wall. Nowadays, parallelism is present at different levels in high performance computing: from instruction decoding and execution (Instruction-Level parallelism, ILP) to the number of interconnected nodes in a cluster or worldwide. From an architectural point of view, parallelism is exhibited in the number of cores etched on a single die. However, increasing the degree of components interconnected brings forward scalability complications. In addition, cores are, nowadays, extremely sophisticated by implementing complex pipelines featuring wide vector length capabilities. In this way, the present Thesis, "Manycore Architectures and SIMD Optimizations for High Performance Computing", addresses these two orthogonal dimensions by analyzing modern manycore architectures and focusing on discovering potential design improvements at two different levels of the architectural stack, and providing techniques for synthesizing efficient platform-aware SIMD code.

## **Objectives and Work Methodology**

The main objectives of this Thesis are listed below, including some key sub-goals.

1. Analysis and modeling of the Intel Xeon Phi x200 (Knights Landing, KNL).

- Analysis and characterization of the core architecture, distributed cache coherence directory and interconnection network.

- Implementation of the Knights Landing architectural model by extending an architectural simulator (Tejas Simulator).

- Experimental assessment of the simulator accuracy by running different workloads.

- 2. Optimizing coherence traffic in manycore architectures.

- Approach to discover the physical layout and location of components.

- Reverse engineering of hash address functions on KNL.

- Runtime- and compile-time-based approaches to optimize the coherence traffic in the interconnection network.

- Evaluation of the static and dynamic approaches proposed.

- 3. Development of a profiling and performance analysis toolkit specifically designed for experiments requiring the configuration of many parameters.

- Automatic compilation, execution and analysis given any set of programs or benchmarks and parameters of interest, e.g., the size of a matrix, the step in a loop, etc.

- Data mining techniques for extracting knowledge from experiments based on the target dimensions, i.e., to quantify the influence of variables.

- Toolkit compatible with any type of application, designed for increasing the productivity, quality, and repeatability of the experiments.

- 4. Synthesis of efficient x86 SIMD code for random vector packing and fusion of reductions.

- Generation of random vector packing combinations using the instructions available given a concrete ISA, based on an SMT model.

- Building of a cost model driven by the empirical performance based on the micro-benchmarking of those combinations for each concrete platform.

- Development of a source-to-source compiler for synthesizing efficient vector code for each platform based on the individual characterization.

- Evaluation using different target applications.

### **Funding and Technical Means**

The means that were used to carry out this Thesis have been the following:

- Working material, human and financial support primarily by the Computer Architecture Group of the University of A Coruña, along with the Research Fellowship funded by the Ministry of Education of Spain (FPU program, ref. FPU16/00816).

- Access to bibliographical material through the library of the University of A Coruña.

- Additional funding through the following research projects:

- Regional funding by the Galician Government (Xunta de Galicia) under the Consolidation Program of Competitive Research Groups (Computer Architecture Group, refs. ED431C 2017/04 and ED431C 2021/30) and Network of Cloud and Big Data Technologies for HPC (ref. ED431D R2016/045).

- State funding by the Ministry of Science and Innovation of Spain through the projects "New Challenges in High Performance Computing: from Architectures to Applications (II)" (ref. TIN2016-75845-P) and "Current Challenges in HPC: Architectures, Software and Applications" (ref. PID2019-104184RB-I00).

- European funding: project "Network for Sustainable Ultrascale Computing" (NESUS COST Action ref. IC1305).

- European Network on High Performance and Embedded Architecture and Compilation (HiPEAC) competitive grant for attending the 13th International Summer School on Advanced Computer Architecture and Compilation for High Performance and Embedded Systems (ACACES 2017).

- Access to clusters, supercomputers and computing platforms:

- Pluton cluster (Computer Architecture Group, University of A Coruña)

featuring 30 nodes with 688 physical cores (1376 threads), including 3

- nodes with Cascade Lake architecture, 4.1 TiB of memory, and 2 many-core accelerators Intel Xeon Phi (Knights Corner).

- Intel Xeon Phi x200 standalone machine (Computer Architecture Group, University of A Coruña).

- Access to a private cluster within the Department of Computer Science at Colorado State University, USA.

- A three-month research visit to Colorado State University. This visit was funded by Inditex-University of A Coruña through a competitive grant under the "inMotion Program".

#### Structure of the Thesis

The Thesis is organized as follows:

- 1. Chapter 1 introduces the main challenges in current high performance computing, presenting the main topics that will be investigated in the Thesis.

- 2. Chapter 2 explores modern manycore architectures and the effect of coherence traffic in the interconnection network. We also perform reverse engineering for obtaining the hash address functions used for distributing data across tiles. Equipped with this information, we propose static and dynamic approaches to leverage this data distribution by improving spatial locality in programs. We conclude this chapter by assessing the solutions proposed, and describing the limitations of our approaches using different sets of benchmarks and applications.

- 3. Chapter 3 continues the topic of the previous chapter by analyzing and modeling a modern manycore architecture (Intel Xeon Phi x200 Knights Landing) and its interconnection network. In this chapter we also describe the development of an extension for the Tejas simulator (a cycle-accurate architectural simulator) based on this model, assessing its accuracy against real hardware.

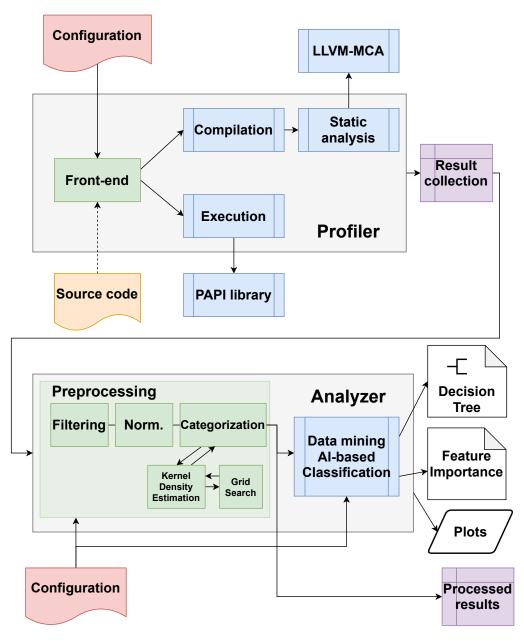

- 4. Chapter 4 presents MARTA, which stands for Multi-configuration Assembly pRofiler and Toolkit for performance Analysis. This is a toolkit developed

for improving productivity and automating error-prone tasks when profiling micro-benchmarks and/or regular applications based on tested-and-true good practices. It also implements data mining and machine learning techniques for analyzing and extracting knowledge from profiling data. We assess its performance with five valuable case studies, and using it for running and profiling benchmarks and applications.

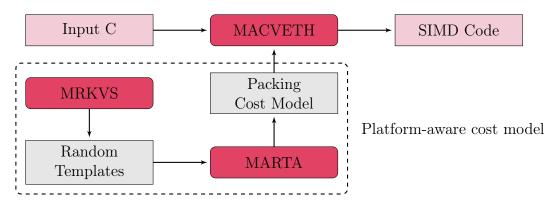

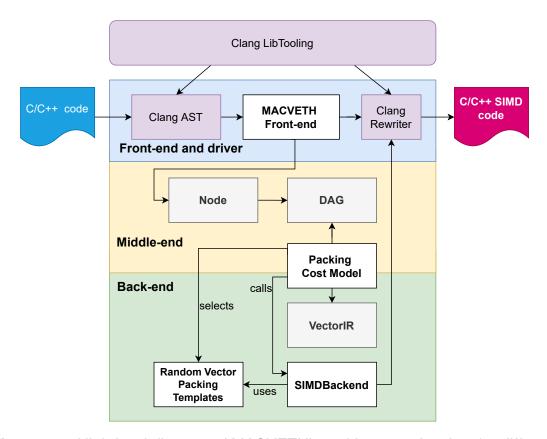

- 5. Chapter 5 proposes novel data packing techniques for random memory addresses into the same vector register, as well as for the fusion of different reductions. For this purpose, we have developed a novel SMT-based system for generating random packing templates based on a given ISA. Leveraging this information, we have built a cost model driven by the empirical performance of those templates on each platform. This model is then used by MACVETH (Multi-Architectural C-VEcTorizer for HPC applications), a novel source-to-source compiler that is able to pack any random set of memory addresses in order to vectorize a set of operations, including reductions. This compiler is also able to pack and fuse independent reductions together. We conclude this chapter assessing the quality and the use cases of our approach.

- 6. Chapter 6 concludes the Thesis discussing some final remarks, and proposing additional research lines that are worth considering as future work.

#### **Main Contributions**

The main original and novel contributions of this Thesis are stated below:

- Development of an extension for the Tejas Simulator to explore the KNL architecture or any other similar one featuring a distributed directory system. This extension allows to analyze the coherence traffic over the interconnection network [44, 46].

- Reverse engineering of the Intel Knights Landing architecture to discover its

physical layout. Based on this, we developed ways to optimize the coherence traffic, the thread-to-core-affinity, and the scheduling of a set of tasks on

the mesh, leveraging the unique characteristics of a particular processor unit stemming from process variations [45].

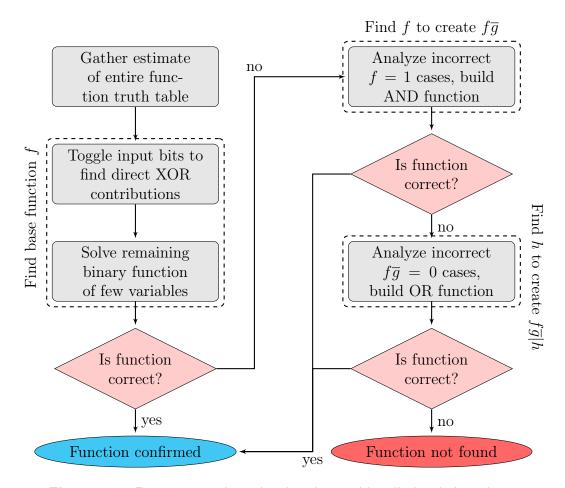

- Uncovering the pseudo-random mapping function of physical memory blocks across the pieces of the distributed directory in KNL. Leveraging this knowledge, candidate optimizations to improve memory latency through the optimization of coherence traffic are studied. Although these optimizations do improve memory throughput, ultimately this does not translate into performance gains due to inherent overheads stemming from the computational complexity of the mapping functions [68].

- Development of MARTA, a toolkit for profiling and performance analysis meant to increase productivity [50, 52]. This toolkit is not a substitute for any other well-known toolkits available, but its main and novel contribution is the emphasis on the automation, improving productivity and quality of results. In an orthogonal dimension, the toolkit also includes a module for performance analysis, using data mining and machine learning techniques.

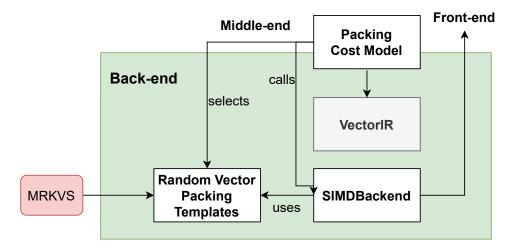

- Development of MRKVS (Mega-Random Kernel Vector SMT), an SMT-based system for generating any random packing template given an ISA. From these templates, we build a cost model for enabling random vector packing.

- Development of MACVETH (Multi-Architectural C-VEcTorizer for HPC applications) [51], a source-to-source compiler for synthesizing efficient SIMD code on specific regions of code featuring patterns with irregular memory accesses. This compiler includes the cost model built with MRKVS, and heuristics for vectorizing the fusion of independent reductions.

#### **Developed Software**

The software libraries and tools developed in this Thesis are publicly available:

• Tejas KNL. Custom implementation of the Intel Knights Landing architecture on the Tejas Simulator. Available at https://github.com/UDC-GAC/tejas\_knl.

- papi\_wrapper: C macro-based library for simplifying the use of the PAPI library. Available at https://github.com/UDC-GAC/papi\_wrapper.

- MARTA: Multi-configuration Assembly pRofiler and Toolkit for performance Analysis. Framework built for increasing productivity and quality of the experiments requiring (micro-)benchmarking and post hoc performance analysis. Available at https://github.com/UDC-GAC/MARTA.

- MRKVS: Mega-Random Kernel Vector SMT. Z3-based [23] system for generating combinations of instructions for packing random data on the same vector register. Available at https://github.com/UDC-GAC/MRKVS.

- MACVETH: Multi-Architectural C-VEcTorizer for HPC applications. Source-to-source C compiler for vectorizing irregular random memory accesses and reductions. Available at https://github.com/UDC-GAC/MACVETH.

#### **Publications from the Thesis**

#### Journal publications

- S. Kommrusch, M. Horro, L.-N. Pouchet, G. Rodríguez, and J. Touriño. Optimizing Coherence Traffic in Manycore Processors Using Closed-Form Caching/Home Agent Mappings. *IEEE Access*, 9:28930–28945, 2021. doi: 10.1109/ACCESS.2021.3058280. JCR Q2 [68].

- M. Horro, G. Rodríguez, and J. Touriño. Simulating the Network Activity of Modern Manycores. *IEEE Access*, 7:81195–81210, 2019. doi: 10.1109/ACCESS.2019.2923855. JCR Q1 [46].

#### International conferences

M. Horro, L.-N. Pouchet, G. Rodríguez, and J. Touriño. MARTA: Multiconfiguration Assembly pRofiler and Toolkit for performance Analysis. Submitted for publication. 2022 [52].

- M. Horro, L.-N. Pouchet, G. Rodríguez, and J. Touriño. MACVETH: Multi-Architectural C-VEcTorizer for HPC applications. Submitted for publication. 2022 [51].

- M. Horro, M. T. Kandemir, L.-N. Pouchet, G. Rodríguez, and J. Touriño. Effect of Distributed Directories in Mesh Interconnects. In *Proceedings of the 56th Annual Design Automation Conference (DAC)*, pages 51:1–6, Las Vegas, NV, USA, 2019. doi: 10.1145/3316781.3317808. Core A. GII-GRIN-SCIE Class 1 [45].

#### **National conferences**

M. Horro, L.-N. Pouchet, G. Rodríguez, and J. Touriño. Toolkit para (Micro-) Benchmarking y Análisis de Características de Rendimiento en Kernels. In Actas XXXI Jornadas de Paralelismo (SARTECO), pages 303–312, Málaga, Spain, 2021 [50].

#### Other minor publications

- M. Horro, L.-N. Pouchet, G. Rodríguez, and J. Touriño. Exploring SIMD Instructions for Packing Random Vector Operands in Modern x86 CPUs. In Proceedings of the 17th International Summer School on Advanced Computer Architecture and Compilation for High-Performance Embedded Systems (ACACES), pages 143–146, Fiuggi, Italy, 2021 [49].

- M. Horro, G. Rodríguez, J. Touriño, and M. T. Kandemir. Study of the Intel Knights Landing (KNL) Memory System Tradeoffs. In Proceedings of the 13th International Summer School on Advanced Computer Architecture and Compilation for High-Performance and Embedded Systems (ACACES), pages 1–4, Fiuggi, Italy, 2017 [44].

# **Contents**

| Preface                                                                                 | XVII  |

|-----------------------------------------------------------------------------------------|-------|

| Contents                                                                                | XXV   |

| List of Tables                                                                          | XXXI  |

| List of Figures                                                                         | XXXV  |

| Listings                                                                                | XXXIX |

| List of Algorithms                                                                      | XLI   |

| 1. Introduction: Challenges in High Performance Computing                               | 1     |

| 2. Effect of Distributed Directories and Optimization of Coherence Traffic in Manycores | 7     |

| 2.1 Introduction                                                                        | . 8   |

|    | 2.2 | Intel Knights Landing (KNL): Xeon Phi x200                     | 10 |

|----|-----|----------------------------------------------------------------|----|

|    |     | 2.2.1 Internal organization                                    | 11 |

|    |     | 2.2.2 Memory system                                            | 13 |

|    |     | 2.2.3 Cluster modes                                            | 15 |

|    |     | 2.2.4 Memory modes                                             | 15 |

|    | 2.3 | Mapping the Knights Landing Processor                          | 15 |

|    | 2.4 | Processor Affinity and Data Layout                             | 19 |

|    | 2.5 | Experimental Results Varying Processor Affinities              | 21 |

|    |     | 2.5.1 Effect of core-to-CHA affinity on memory latency         | 22 |

|    |     | 2.5.2 Effect of thread-to-core affinity on coherence traffic   | 22 |

|    |     | 2.5.3 Optimized thread-to-core scheduling                      | 24 |

|    | 2.6 | Reverse Engineering the CHA Mapping                            | 27 |

|    | 2.7 | Runtime Optimization                                           | 34 |

|    |     | 2.7.1 Experimental results                                     | 37 |

|    | 2.8 | Compile-time Optimization                                      | 40 |

|    |     | 2.8.1 Fixing physical addresses                                | 45 |

|    |     | 2.8.2 Experimental results                                     | 46 |

|    | 2.9 | Discussion and Related Work                                    | 50 |

| 3. | Si  | mulating the Network Activity of Modern Manycore Architectures | 55 |

|    | 3.1 | Introduction                                                   | 56 |

|    | 3.2 | Overview and Motivation                                        | 57 |

| 3.3 | Tejas Simulator: Architecture and Extensibility                                   | 59 |

|-----|-----------------------------------------------------------------------------------|----|

|     | 3.3.1 Front-end: the emulator                                                     | 59 |

|     | 3.3.2 Back-end: the simulation engine                                             | 61 |

| 3.4 | Modeling KNL in Tejas                                                             | 64 |

|     | 3.4.1 Tiles and cores                                                             | 64 |

|     | 3.4.2 Memory system                                                               | 65 |

|     | 3.4.3 Interconnection network                                                     | 67 |

|     | 3.4.4 Other considerations                                                        | 68 |

| 3.5 | Validation                                                                        | 68 |

|     | 3.5.1 Experimental setup                                                          | 69 |

|     | 3.5.2 Results                                                                     | 70 |

| 3.6 | Case Study: Analysis of Coherence Traffic Optimizations                           | 76 |

| 3.7 | Related Work                                                                      | 80 |

| 3.8 | Conclusions and Future Work                                                       | 82 |

|     | ARTA: Multi-configuration Assembly pRofiler and Toolkit for per-<br>ance Analysis | 85 |

| 4.1 | Overview and Motivation                                                           | 86 |

| 4.2 | MARTA: System's Architecture                                                      | 88 |

|     | 4.2.1 Profiler                                                                    | 88 |

|     | 4.2.2 Analyzer                                                                    | 90 |

| 4.3 | Measurement Methodology                                                           | 93 |

|     | 4.3.1 Machine configuration                                                       | 94 |

|     | 4.3.2 Repeating runs                                                              | 94 |

|                       | 4.3.3 Measuring CPU performance                                                       | 95                                           |

|-----------------------|---------------------------------------------------------------------------------------|----------------------------------------------|

| 4.4                   | Configuration                                                                         | 96                                           |

|                       | 4.4.1 Profiler                                                                        | 96                                           |

|                       | 4.4.2 Analyzer                                                                        | 01                                           |

| 4.5                   | Evaluation: Case Studies                                                              | 02                                           |

|                       | 4.5.1 Micro-benchmarking gather                                                       | 03                                           |

|                       | 4.5.2 Empirical throughput of FMA instructions                                        | 08                                           |

|                       | 4.5.3 Influence of access pattern on memory bandwidth                                 | 12                                           |

|                       | 4.5.4 Auto-vectorizing reductions                                                     | 15                                           |

|                       | 4.5.5 Cost model for loop permutation                                                 | 19                                           |

| 4.6                   | Related Work1                                                                         | 23                                           |

|                       |                                                                                       |                                              |

| 4.7                   | Discussion and Concluding Remarks1                                                    | 26                                           |

|                       |                                                                                       | 26                                           |

|                       | MD Optimizations: Random Vector Packing and Reduction Fu-                             | 26                                           |

| 5. SI<br>sion         | MD Optimizations: Random Vector Packing and Reduction Fu-                             | 29                                           |

| <b>5. SI sion</b> 5.1 | MD Optimizations: Random Vector Packing and Reduction Fu-                             | 29                                           |

| <b>5. SI sion</b> 5.1 | MD Optimizations: Random Vector Packing and Reduction Fu-  1  Overview and Motivation | 29<br>30<br>33                               |

| <b>5. SI sion</b> 5.1 | MD Optimizations: Random Vector Packing and Reduction Fu-  1  Overview and Motivation | 29<br>30<br>33                               |

| <b>5. SI sion</b> 5.1 | MD Optimizations: Random Vector Packing and Reduction Fu-  Overview and Motivation    | 29<br>30<br>33<br>34<br>36                   |

| <b>5. SI sion</b> 5.1 | MD Optimizations: Random Vector Packing and Reduction Fu-  Overview and Motivation    | 29<br>30<br>33<br>34<br>36<br>40             |

| <b>5. SI sion</b> 5.1 | MD Optimizations: Random Vector Packing and Reduction Fu-  Overview and Motivation    | 29<br>30<br>33<br>34<br>36<br>40<br>44       |

| 5. SI sion 5.1 5.2    | MD Optimizations: Random Vector Packing and Reduction Fu-  Overview and Motivation    | 29<br>30<br>33<br>34<br>36<br>40<br>44<br>45 |

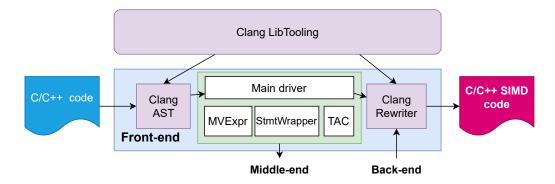

|       | 5.3.2 High-level architecture of MACVETH                     | .153 |

|-------|--------------------------------------------------------------|------|

|       | 5.3.3 Front-end: the driver for parsing and rewriting        | .153 |

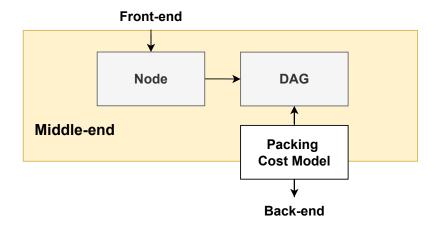

|       | 5.3.4 Middle-end: identifying and grouping reductions        | .158 |

|       | 5.3.5 Back-end: fusing reductions and synthesis of SIMD code | .166 |

|       | 5.3.6 Current limitations of the tool                        | .172 |

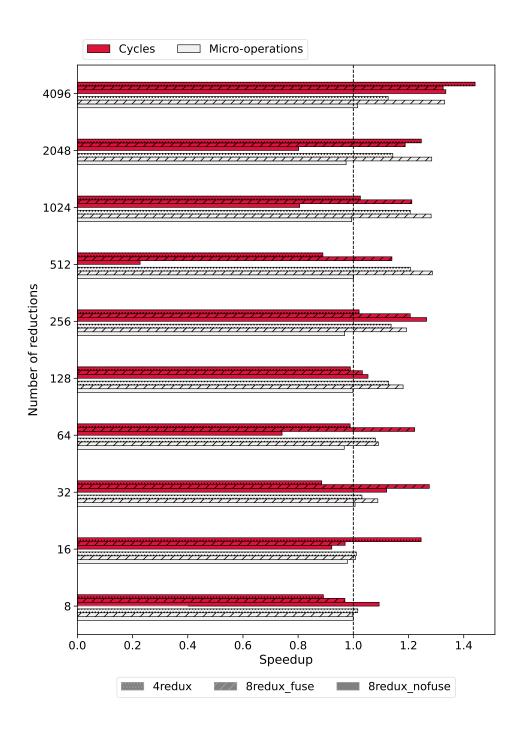

| 5.4   | Experimental Results                                         | .173 |

|       | 5.4.1 Synthetic patterns                                     | .175 |

|       | 5.4.2 Sparse matrices: SuiteSparse repository                | .181 |

| 5.5   | Related Work                                                 | .192 |

| 5.6   | Concluding Remarks and Discussion                            | .194 |

|       |                                                              |      |

| 6. C  | oncluding Remarks and Future Work                            | 197  |

| 6.1   | Conclusions and Discussion                                   | .197 |

| 6.2   | Future Work                                                  | .200 |

|       |                                                              |      |

| Bibli | ography                                                      | 203  |

| A. M  | IARTA Configuration                                          | 223  |

| A.1   | CLI Options                                                  | .223 |

| A.2   | 2 C Macros/Directives                                        | .226 |

|       |                                                              |      |

| B. R  | andom Vector Packing: Instructions                           | 229  |

| B.1   | Load Instructions                                            | .229 |

| B 2   | 2 Swizzle Instructions                                       | 230  |

| XXX | Contents |

|-----|----------|

| C. MACVETH Configuration      | 231 |

|-------------------------------|-----|

| C.1 CLI Options               | 231 |

| C.2 Pragma Options            | 233 |

| C.3 Matrices Used             | 234 |

| D. Resumo Estendido en Galego | 239 |

| Alphabetical Index            | 251 |

# **List of Tables**

| 2.1 Benchmarks used for the optimized thread-to-core scheduling experiments                                                                           | 25 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 Applications in each mix of workloads                                                                                                             | 26 |

| 2.3 Address-to-CHA mapping for the first 128 CHA values out of 256 million                                                                            | 28 |

| 2.4 CHA $_0$ toggle frequency when toggling address bits $a_6$ to $a_{34}$                                                                            | 31 |

| 2.5 For CHA <sub>0</sub> , bits 33 to 30 do not directly get XOR'ed with other bits, but are part of a function that itself is XOR'ed with those bits | 31 |

| 2.6 CHA <sub>2</sub> for the first 256 cache lines                                                                                                    | 33 |

| 3.1 Tejas configuration for modeling tiles in the KNL architecture                                                                                    | 65 |

| 3.2 Tejas configuration for modeling the KNL NoC                                                                                                      | 68 |

| 3.3 Experimental setup for our KNL implementation                                                                                                     | 69 |

| 3.4 Equivalence between the event to measure, the PAPI event, and the event programmed in Tejas                                                       | 70 |

| 3.5 PolyBench/C results for our model                                                                                                                 | 74 |

| 3.6 Parboil results for our model                                                                                                                     | 76 |

| 3.7 Events for the executions of the modified jacobi-1d stencil by thread 0 for Tejas KNL                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.1 Description of all available options within each kernel dictionary in the configuration file for the Profiler                                  |

| 4.2 Description of all available options within each finalize dictionary in the configuration file for the Profiler                                |

| 4.3 Description of all available options within each configuration dictionary in the configuration file for the Profiler                           |

| 4.4 Description of all available options within each compilation dictionary in the configuration file for the Profiler                             |

| 4.5 Description of all available options within each d_features dictionary in the configuration file for the Profiler                              |

| 4.6 Description of all available options within each execution dictionary in the configuration file for the Profiler                               |

| 4.7 Description of all available options within each output dictionary in the configuration file for the Profiler                                  |

| 4.8 Description of all available options within each kernel dictionary in the configuration file for the Analyzer                                  |

| 4.9 Description of all available options within each prepare_data dictionary in the configuration file for the Analyzer                            |

| 4.10 Description of all available options within each plot dictionary in the configuration file for the Analyzer                                   |

| 5.1 MACVETH configurations for the synthetic patterns                                                                                              |

| 5.2 Comparison of MACVETH configurations for the synthetic patterns in terms of speedup in cycles                                                  |

| 5.3 Comparison of MACVETH configurations for the synthetic patterns in terms of speedup in the reduction of the number of micro-operations retired |

| 5.4 Comparison of MACVETH configurations for the synthetic patterns in terms of increment of vector FLOPs issued over the auto-vectorized version181 |

|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.5 MACVETH configurations for the SuiteSparse matrices selected182                                                                                  |

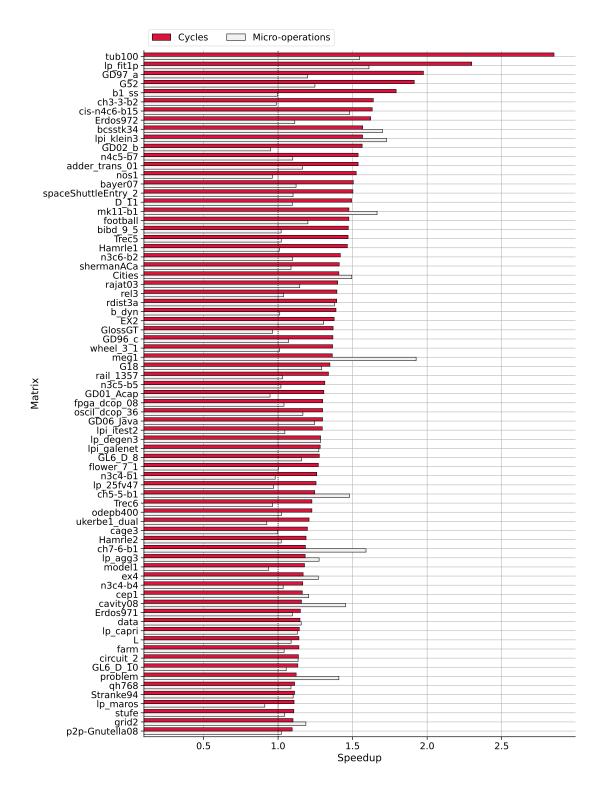

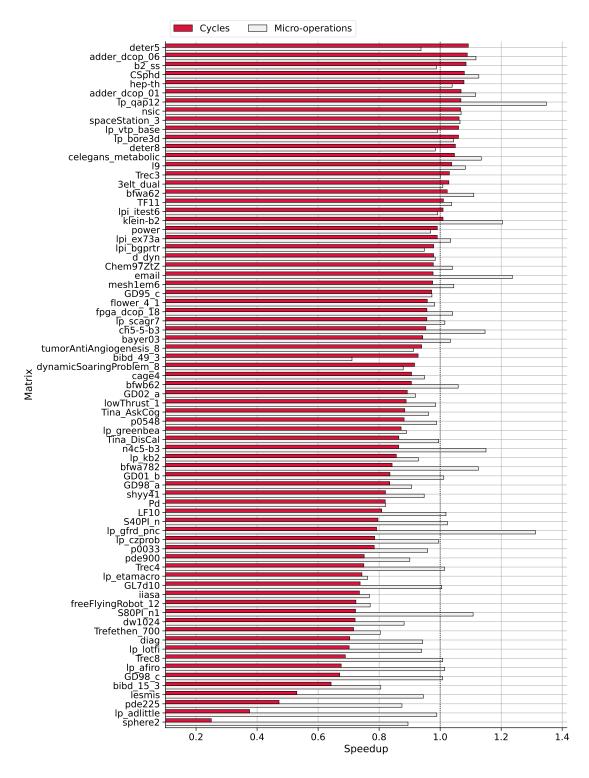

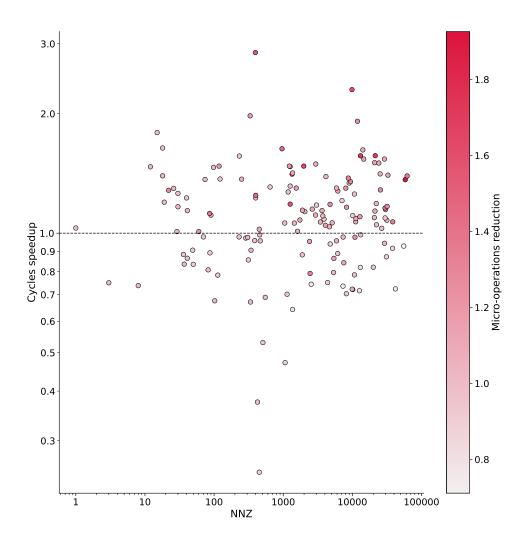

| 5.6 Comparison of MACVETH configurations for the set of matrices in terms of speedup in cycles                                                       |

| 5.7 Comparison of MACVETH configurations for the set of matrices in terms of speedup in the reduction of the number of micro-operations retired      |

| 5.8 Comparison of MACVETH configuration for the set of matrices in terms of increment of vector FLOPs issued over the auto-vectorized version        |

| 5.9 Speedups with MACVETH for the large matrices using the 4redux_noorphan_fuse MACVETH configuration192                                             |

| A.1 Macros included in MARTA                                                                                                                         |

| B.1 Load instructions for the float data type considered in our model229                                                                             |

| B.2 Swizzle instructions for the float data type considered in our model 230                                                                         |

| C.1 Sparse matrices used for the experiments from SuiteSparse234                                                                                     |

## **List of Figures**

| 2.1 Traditional memory fileratory updated with new emerging technologies                                                                 | 11 |

|------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 High-level tile organization in KNL                                                                                                  | 12 |

| 2.3 Intel KNL floorplan. Cache miss flow for Quadrant cluster mode                                                                       | 14 |

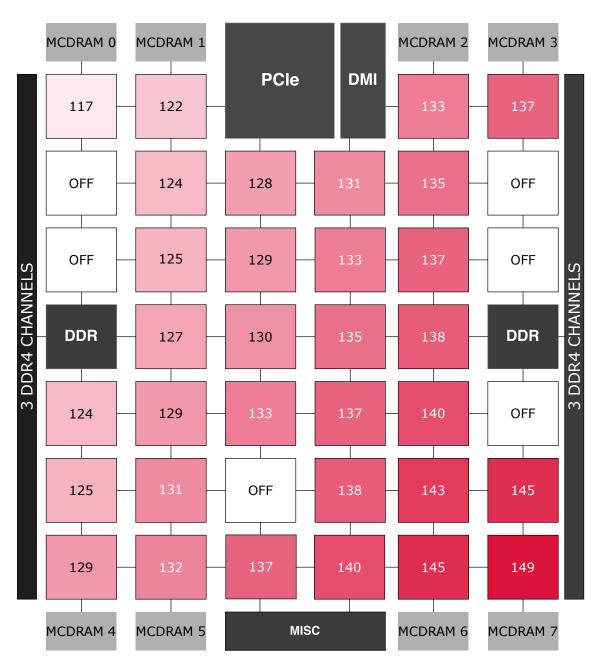

| 2.4 Floorplan reconstructed from our model for KNL                                                                                       | 20 |

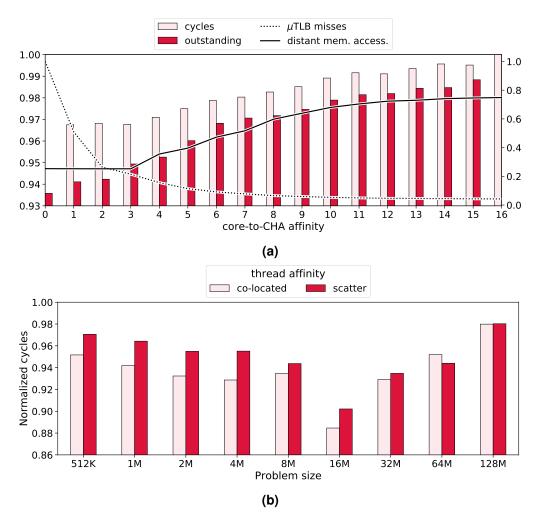

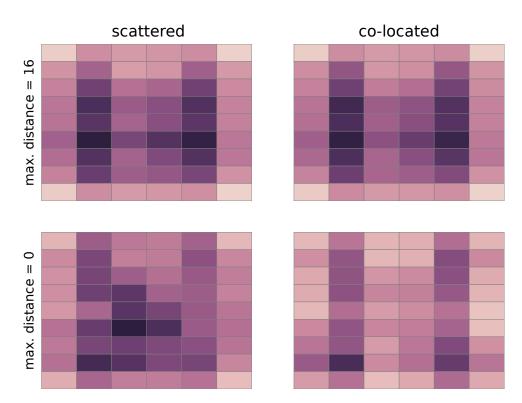

| 2.5 Effects of core-to-CHA and thread-to-core affinities                                                                                 | 23 |

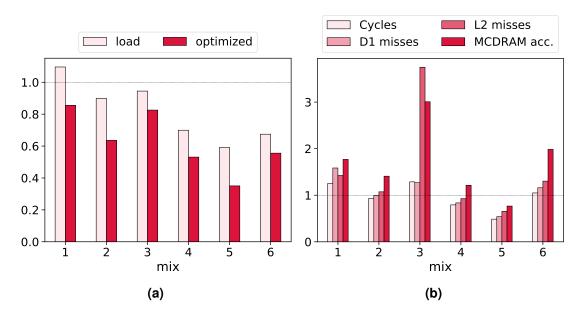

| 2.6 Results of optimized scheduling strategies                                                                                           | 27 |

| 2.7 Reverse engineering hardware-friendly hash functions                                                                                 | 29 |

| 2.8 Reverse-engineered mapping function between memory blocks and CHAs                                                                   | 32 |

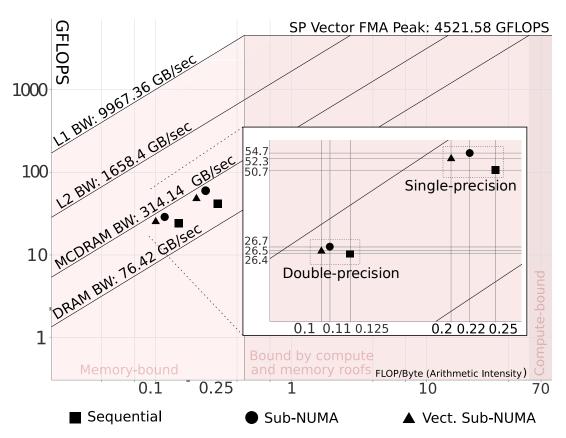

| 2.9 Roofline plot for the matrix-vector multiplication using both single- and double-precision arithmetic                                | 38 |

| 2.10 Sum of selected performance counters for all threads                                                                                | 39 |

| 2.11 Sets of regular subcomputations built for the Sparse Matrix-Vector Multiplication of matrix FIDAP/ex7 in the SuiteSparse repository | 41 |

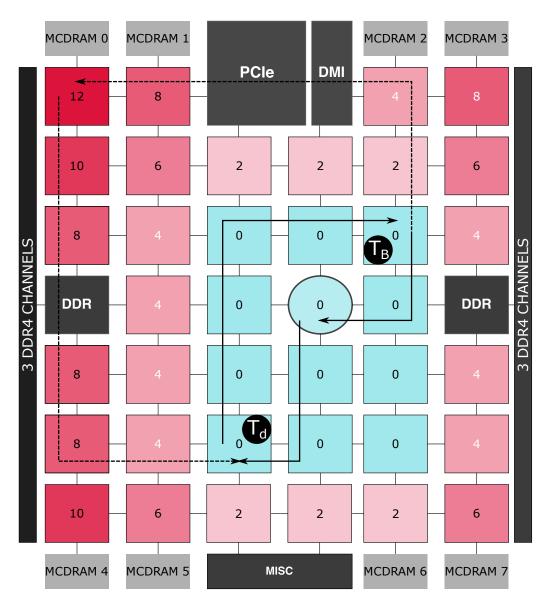

| 2.12 Overhead, in mesh cycles, of accessing a block of data resident in the L2 cache of tile $T_B$ , and with coherence information resident in tile $T_d$ | 43 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

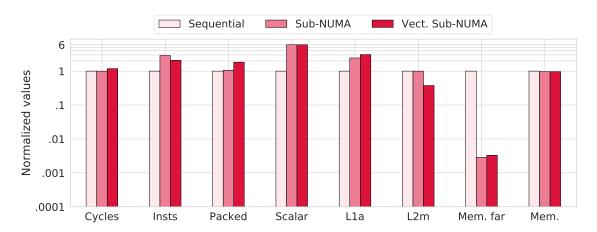

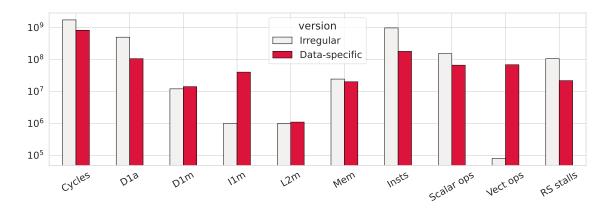

| 2.13 Performance counters for irregular and data-specific versions of the SpMV operation                                                                   | 48 |

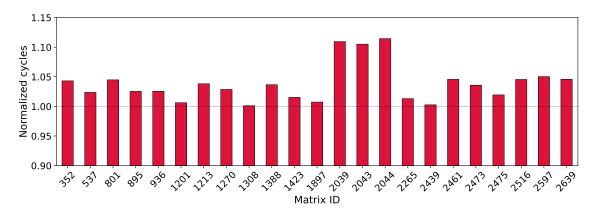

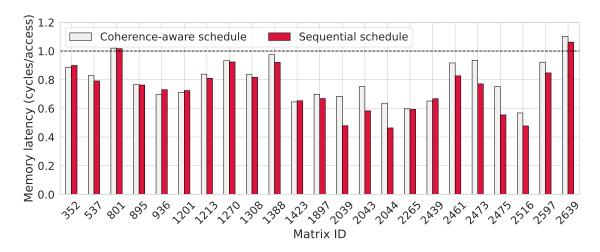

| 2.14 Execution cycles of the coherence-aware schedule, normalized to those of the sequential schedule. Note that the Y axis is truncated for readability   | 48 |

| 2.15 Performance counters for selected matrices in the experimental setup                                                                                  | 49 |

| 2.16 Memory latency of the coherence-aware schedule normalized to the sequential schedule baseline for all the matrices in the experimental setup          | 50 |

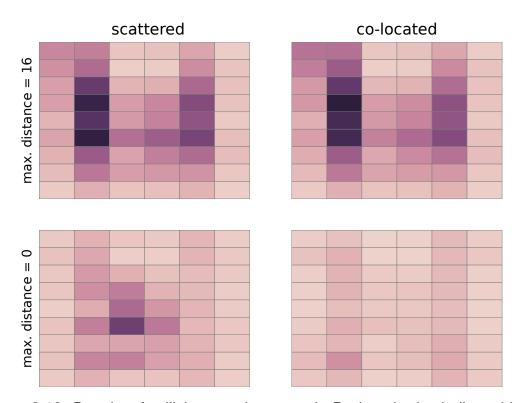

| 3.1 Floorplan of the Intel KNL and heatmap of the measured latency                                                                                         | 58 |

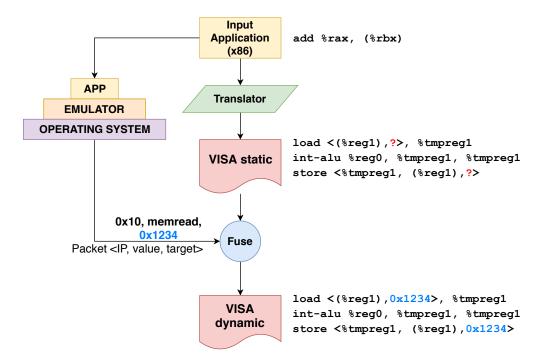

| 3.2 Translation process in Tejas from the binary instrumentation to the VISA                                                                               | 60 |

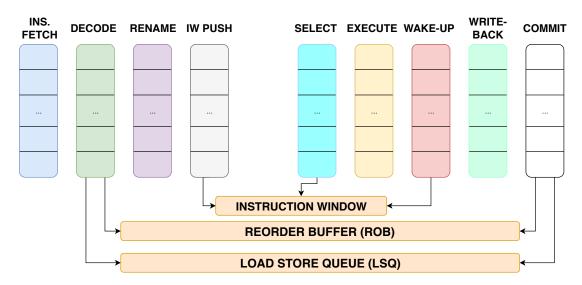

| 3.3 Stages and main registers of the Out-of-Order pipeline in Tejas                                                                                        | 62 |

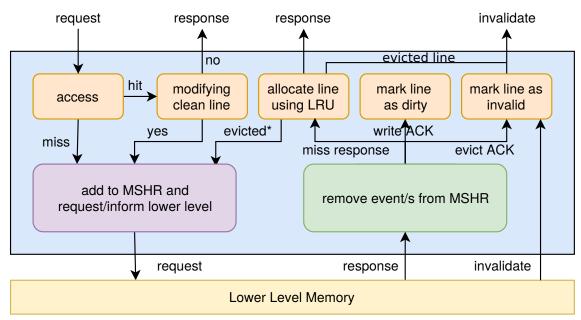

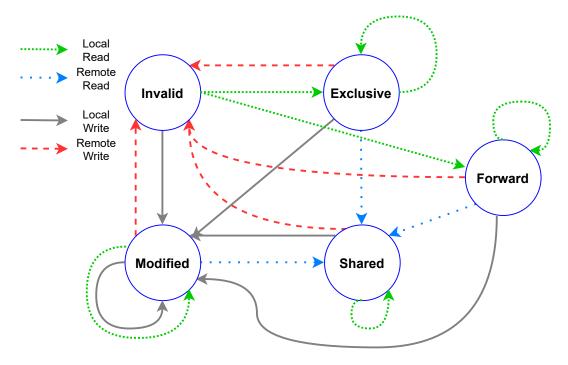

| 3.4 Cache behavior in Tejas                                                                                                                                | 63 |

| 3.5 MESIF protocol implementation based on MESI                                                                                                            | 67 |

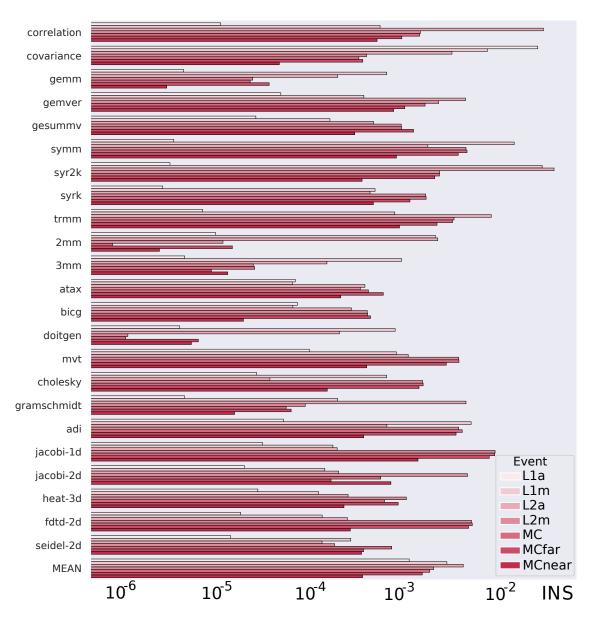

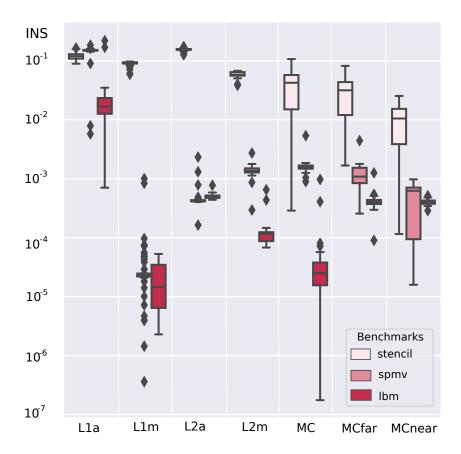

| 3.6 INS error metric for PolyBench/C benchmarks                                                                                                            | 72 |

| 3.7 INS error metric for Parboil benchmarks                                                                                                                | 75 |

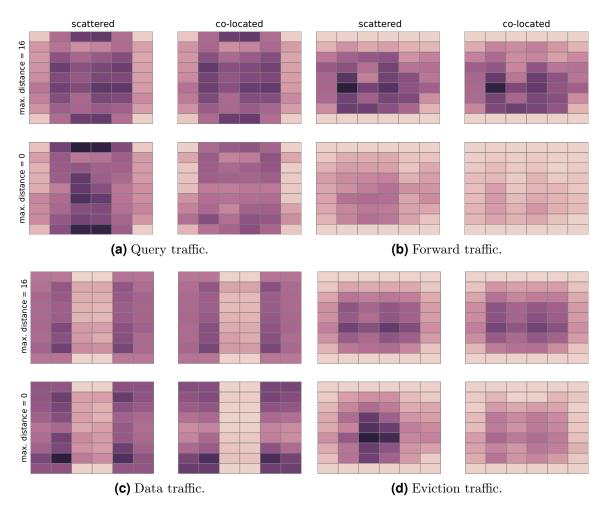

| 3.8 Heatmap of the number of packets across the mesh for Tejas KNL                                                                                         | 78 |

| 3.9 Breakdown of the different packet types across the NoC for Tejas KNL                                                                                   | 80 |

| 3.10 Density of collisions on the network for Tejas KNL                                                                                                    | 81 |

| 4.1 High-level architecture of the MARTA toolkit                                                                                                           | 89 |

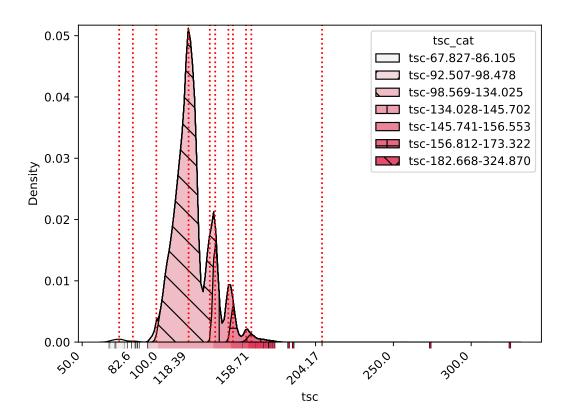

| 4.2 Distribution plot regarding performance for gather experiments10                                                                                       | 06 |

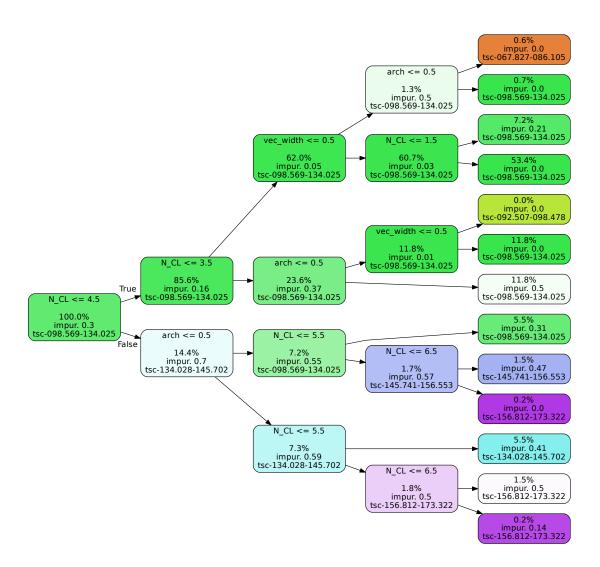

| 4.3 Decision tree generated for the gather experiment                                                                                                      | 07 |

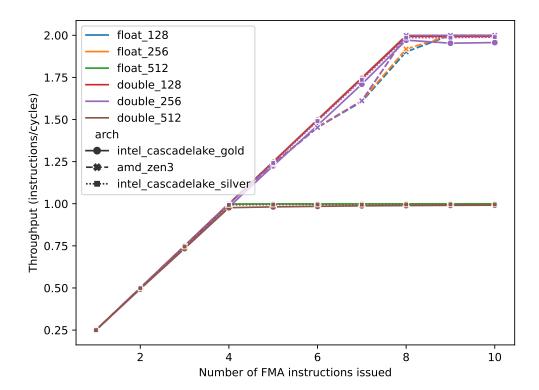

| 4.4 Line plot generated by MARTA for the FMA throughput experiment1                                                                                        | 11 |

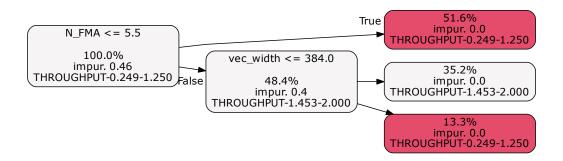

| 4.5 Simple predictor synthesized by MARTA1                                                                                                                 | 12 |

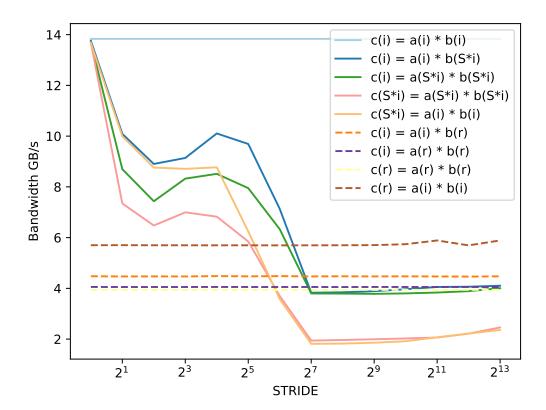

| 4.6 Bandwidth obtained for different access patterns using a single thread115                    |

|--------------------------------------------------------------------------------------------------|

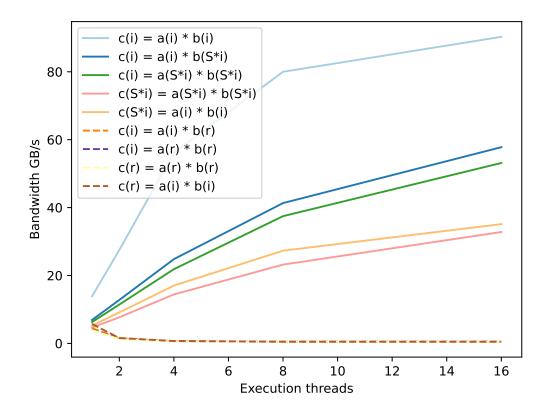

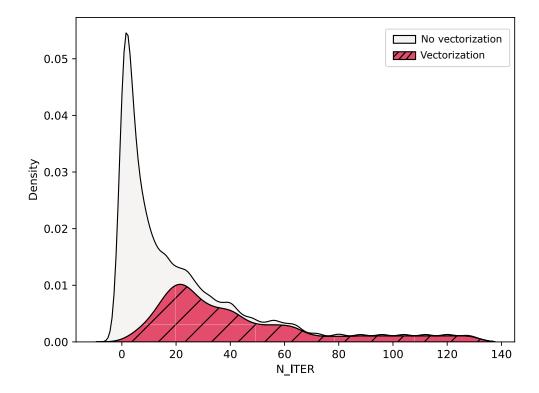

| 4.7 Multithreaded bandwidth per stream version116                                                |

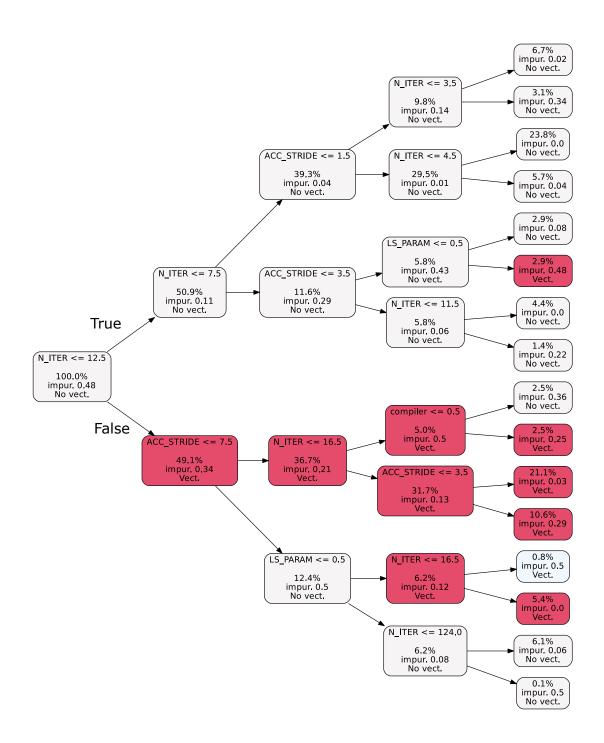

| 4.8 Stacked density graph for the auto-vectorization experiment using MARTA119                   |

| 4.9 Decision tree obtained for the auto-vectorization experiment120                              |

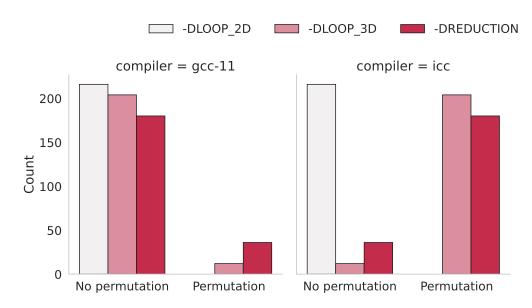

| 4.10 Distribution plot for the loop permutation experiment                                       |

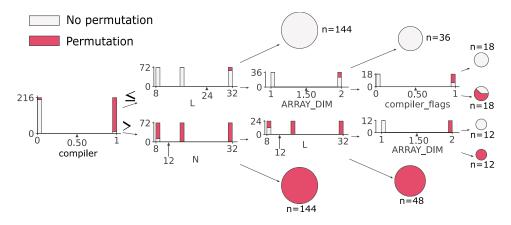

| 4.11 Decision tree built by MARTA for the -DLOOP_3D kernel for the loop permutation experiment   |

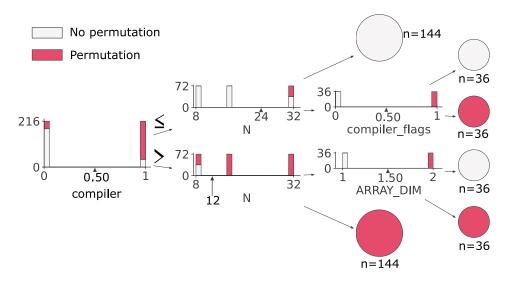

| 4.12 Decision tree built by MARTA for the -DREDUCTION kernel for the loop permutation experiment |

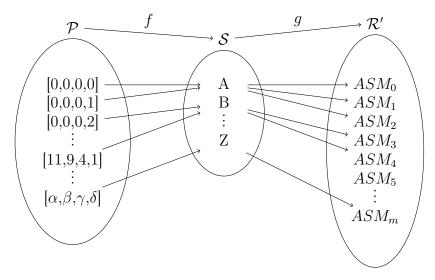

| 5.1 High-level picture of the inter-operation between the components presented in the Thesis     |

| 5.2 Functions and sets defined in the system                                                     |

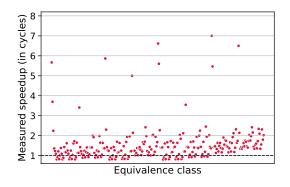

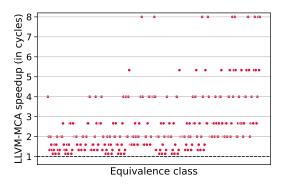

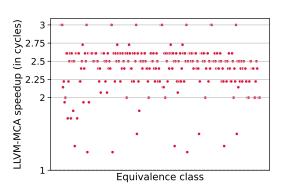

| 5.3 Speedups (in cycles) obtained for Intel Cascade Lake                                         |

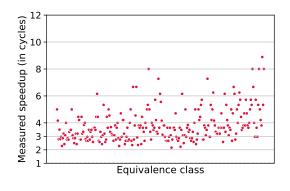

| 5.4 Speedups (in cycles) obtained for AMD Zen3148                                                |

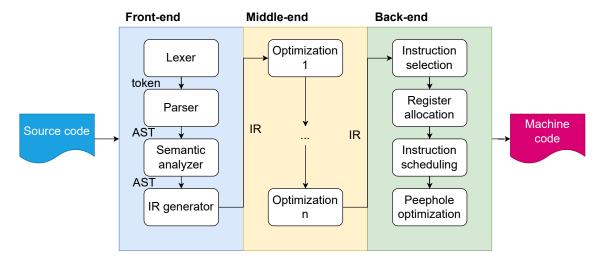

| 5.5 Classic high-level diagram of the compiler architecture                                      |

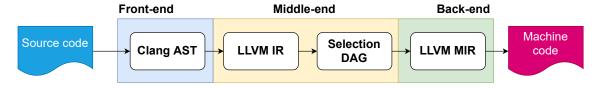

| 5.6 High-level LLVM toolchain                                                                    |

| 5.7 High-level diagram of MACVETH's architecture                                                 |

| 5.8 MACVETH's front-end components                                                               |

| 5.9 MACVETH's middle-end components159                                                           |

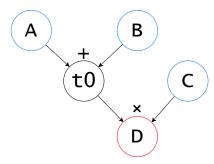

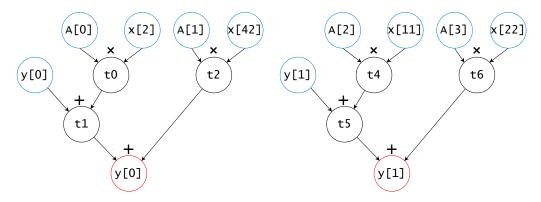

| 5.10 DAG generated from the example in Listing 5.6                                               |

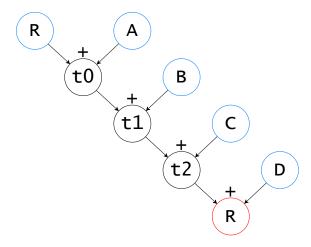

| 5.11 DAG generated from the reduction TACs in Listing 5.7b                                       |

| 5.12 DAG generated from the reduction TACs in Listing 5.8b                                       |

| 5.13 MACVETH's back-end components                                                               |

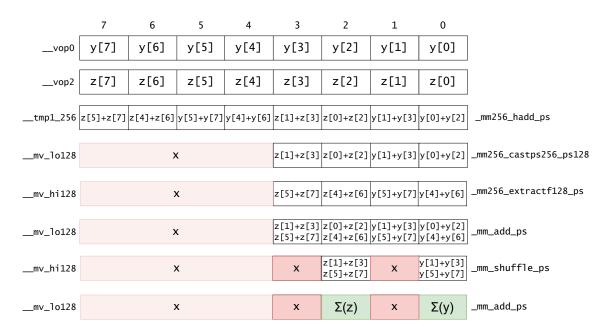

| 5.14 Graphic description of vectors' content for the code in Listing 5.12b170                    |

| 5.15 Graphic description of vectors' content for the code in Listing 5.13b171                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

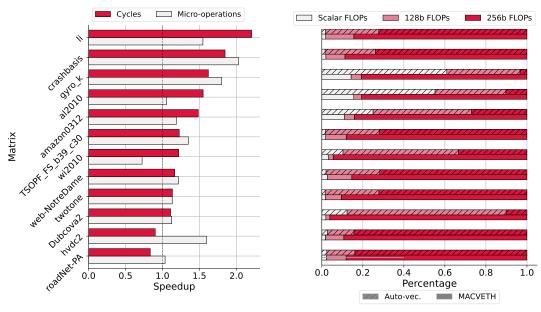

| 5.16 Speedups obtained in cycles and in the reduction of the number of micro-<br>operations for the synthetic patterns for all MACVETH configurations                                        |

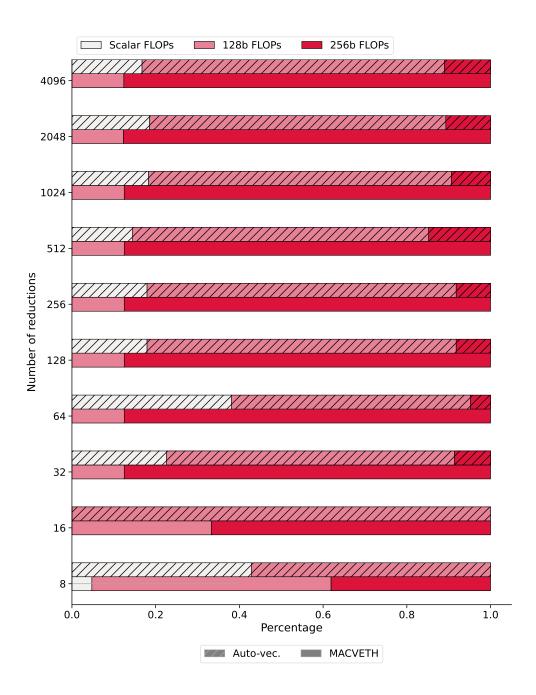

| 5.17 Percentage of scalar and vector FLOPs for the synthetic patterns with the GCC auto-vectorized version and the <code>8redux_fuse</code> MACVETH configuration180                         |

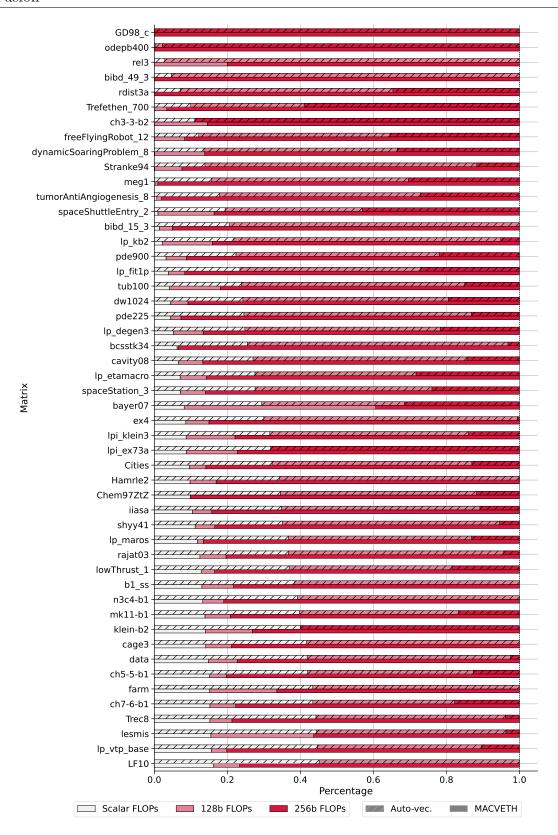

| 5.18 Speedups obtained for the 4redux_noorphan_fuse configuration for the 150 matrices (under 62K NNZ) selected (Part I)                                                                     |

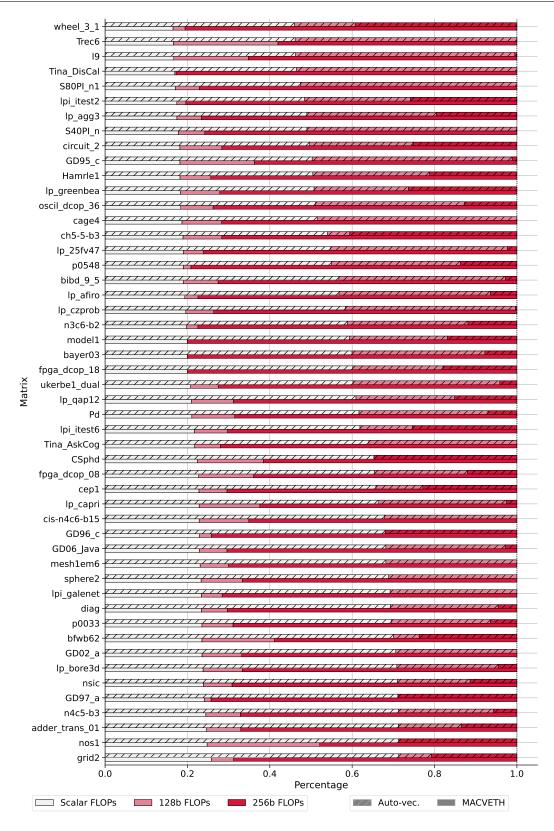

| 5.19 Speedups obtained for the 4redux_noorphan_fuse configuration for the 150 matrices (under 62K NNZ) selected (Part II)                                                                    |

| 5.20 Speedups obtained for the 4redux_noorphan_fuse configuration for the 150 matrices (under 62K NNZ) selected according to the NNZ values of the matrix and the micro-operations reduction |

| 5.21 Percentage of scalar and vector FLOPs for the 150 matrices (under 62K NNZ) selected with the GCC auto-vectorized version and the 4redux_noorphan_fuse MACVETH configuration (Part I)    |

| 5.22 Percentage of scalar and vector FLOPs for the 150 matrices (under 62K NNZ) selected with the GCC auto-vectorized version and the 4redux_noorphan_fuse MACVETH configuration (Part II)   |

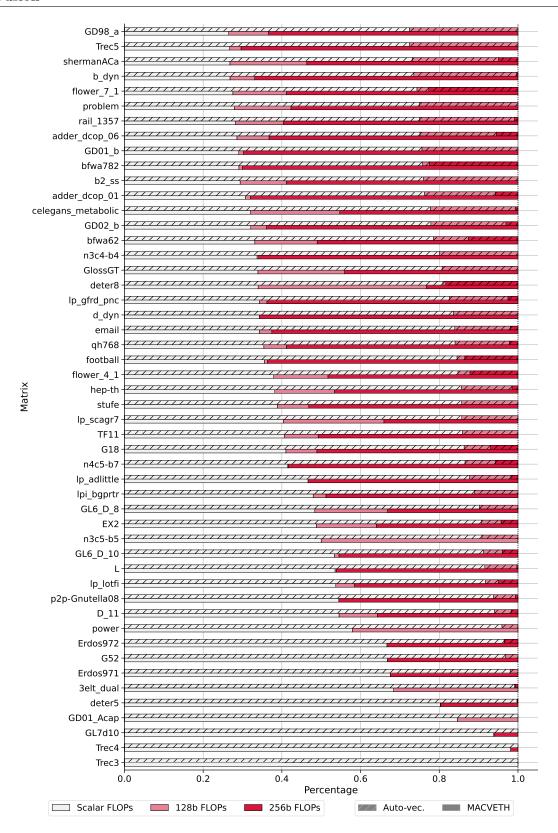

| 5.23 Percentage of scalar and vector FLOPs for the 150 matrices (under 62K NNZ) selected with the GCC auto-vectorized version and the 4redux_noorphan_fuse MACVETH configuration (Part III)  |

| 5.24 Results obtained for the <code>4redux_noorphan_fuse MACVETH</code> configuration for large sparse matrices (>1M NNZ)                                                                    |

### Listings

| ∠. I | Scalar code for general matrix-vector multiplication parallelized using a static |    |

|------|----------------------------------------------------------------------------------|----|

| bloc | k schedule                                                                       | 35 |

| 2.2  | Manually vectorized code for general matrix-vector multiplication parallelized   |    |

| usin | g a static block schedule                                                        | 38 |

| 2.3  | Classic irregular SpMV code                                                      | 46 |

| 4.1  | Toy example of a benchmark using macros included in MARTA                        | 00 |

| 4.2  | Input C code for the gather experiment                                           | 04 |

| 4.3  | Assembly code generated for the gather experiment                                | 05 |

| 4.4  | Configuration required for the FMA experiment1                                   | 10 |

| 4.5  | AVX triad kernel used for measuring memory bandwidth1                            | 13 |

| 4.6  | Vectorizable reduction of N floating-point values                                | 17 |

| 4.7  | Code for benchmarking a single vector-constant multiplication reduction 1        | 18 |

| 4.8  | 3-dimensional loop nest benefiting from loop permutation                         | 21 |

| 4.9  | Simplified input source code to explore loop permutation with MARTA              | 23 |

| 5.1  | Ad hoc SIMD instructions to consider in our model                                | 36 |

| 5.2  | Python code used in the x86-sat system1                                          | 42 |

| 5.3  | Example of the cascadelake_avx2_float_n4_0_0.mrt template1                       | 45 |

| 5.4  | Candidates generated by MRKVS for packing three non-contiguous ele-              |    |

| men  | nts1                                                                             | 47 |

| 5.5  | Assembly code generated for the example in Listing 5.4                           | 47 |

| 5.6 TAC translation for $D = (A + B) * C$                                     | 158 |

|-------------------------------------------------------------------------------|-----|

| 5.7 TAC translation for 4 reductions                                          | 159 |

| 5.8 TAC translation for the SpMV code                                         | 162 |

| 5.9 Example code where the grouping of orphan reduction nodes applies         | 166 |

| 5.10 Example of synthesis in MACVETH for 4 reductions on a float in SSE       |     |

| (AVX2-compliant)                                                              | 168 |

| 5.11 Example of synthesis in MACVETH for 8 reductions on a float in AVX2      | 168 |

| 5.12 Example of synthesis in MACVETH for the fusion of two independent re-    |     |

| ductions of 4 elements each within the same vector                            | 170 |

| 5.13 Example of synthesis in MACVETH for the fusion of two independent re-    |     |

| ductions of 8 elements each in two different vectors                          | 171 |

| 5.14 Classic SpMV kernel using CSR format                                     | 173 |

| 5.15 Computations generated with the system developed by Augustine et al. for |     |

| the input matrix JGD_Kocay/Trec5 from the SuiteSparse collection              | 174 |

| 5.16 Loop present in the synthetic codes generated                            | 176 |

| C.1 Pragmas required to indicate the regions of interest for MACVETH          | 233 |

# **List of Algorithms**

| 2.1 | Measures latencies for a $(C, CH, MC)$ tuple                          | 18  |

|-----|-----------------------------------------------------------------------|-----|

| 2.2 | Static scheduling of SpMV operations                                  | 44  |

| 4.1 | Approach for collecting data from executions in MARTA                 | 91  |

| 4.2 | High-level approach of MARTA's execute function                       | 92  |

| 5.1 | High-level approach of the MRKVS system                               | 143 |

| 5.2 | recursive_search function used to generate the exploration space in   |     |

|     | MRKVS                                                                 | 144 |

| 5.3 | translateStmtToTAC recursive function to translate statements into    |     |

|     | TAC format                                                            | 157 |

| 5.4 | Unrolling for a list of TACs                                          | 158 |

| 5.5 | Approach followed by MACVETH for packing reductions                   | 163 |

| 5.6 | $vectorize\_orphan\_redux$ function for vectorizing orphan reductions | 165 |

-Engineer at the Advanced Computing Systems Division of IBM commenting on the nascent microchip in 1968

1

# Introduction: Challenges in High Performance Computing

"The complexity for minimum component costs has increased at a rate of roughly a factor of two per year (...). Certainly over the short term this rate can be expected to continue, if not to increase. Over the longer term, the rate of increase is a bit more uncertain, although there is no reason to believe it will not remain nearly constant for at least 10 years. That means by 1975, the number of components per integrated circuit for minimum cost will be 65,000."

- Gordon E. Moore [94]

It has been more than fifty five years, in April 1965, since Gordon Moore was first asked to predict the evolution of semiconductors in the following years. He is one of the "traitorous eight" who left Shockley Semiconductor Laboratory to found Fairchild Semiconductors in 1957. There, just a couple of years later, Robert Noyce, also co-founder, invented the planar integrated circuit. Moore, by observing electronics trends and the pace followed by semiconductor industry in the previous years, predicted that the number of components on those integrated circuits would double every year for the next decade. This "simple" forecast became prophecy. Just three years later, in 1968, he co-founded with, again, Robert Noyce a new company

named NM Electronics, which was later renamed as Intel Corporation. Another spin-off from Fairchild, Advanced Micro Devices (AMD), was also founded a year later. That decade passed, and it was in 1975 when he revised again his prognosis adjusting the increase rate to be doubling every two years, establishing what we have studied and known as "Moore's Law", due to its accuracy. Nevertheless, this prediction is commonly quoted to be doubling every eighteen months; but that was never stated by Moore [54].

The extraordinary linearity in the prediction led to an incredible growth in industry, as manufacturing costs dropped rapidly. In such way, technology started to reach the masses. From those 65,000 components in the seventies, we have reached more than 2.6 trillion or  $2.6 \times 10^{12}$  (>  $3 \times 10^7 \times 65,000$ ) transistors on a single die by 2021 [123]. Nevertheless, cramming more components onto integrated circuits was not the only cause for this incredible growth.

Moore's Law was stated from an economic perspective first, although soon was correlated with performance as smaller transistors could switch at higher speeds, i.e., clock frequencies could be increased without incurring timing errors. Nonetheless, frequencies have not increased at the same rate as transistors have shrunk. Dennard's scaling states, in a nutshell, that power density remains constant as transistors shrink. This statement was based on MOSFET design power equations, as described and simplified in Equation 1.1, which establishes a relation between power dissipated (P), switching gate frequency (F), drain voltage  $(V_{dd})$  and dynamic capacitance (C), a factor depending on manufacturing process; being  $\alpha$  the switching activity factor.

$$P = \alpha CFV_{dd}^2 \tag{1.1}$$

An important aspect of Dennard's scaling is that as transistors got smaller the voltage could be reduced, enabling chips to operate at higher frequencies, remaining that power density constant in all chip area. But only these equations ignored two certainly important and limiting factors: the minimal threshold voltage and the leakage current. The first one establishes the minimum amount of potential needed to have a transistor turned on without misfunction. The second one poses difficulties for safe thermal dissipation, narrowing the budget of active transistors supported the

same interval of time. These inabilities or limitations establish what is commonly referred to as the "power wall".

It is debatable, and out of the scope of this Thesis, whether Moore's Law has withered or not, or how long it will hold, but it is clear that with Dennard's scaling breakdown trends in micro-architecture have changed. Frequency is no longer the key factor in terms of performance improvements as recent advances in GPU performance have demonstrated [28], motivating the development of new approaches for reaching Exascale milestone, such as dark silicon or energy-aware solutions, heterogeneous, reconfigurable, and manycore architectures. These last ones are the most promising candidates as they pack within the same processor an interconnection network with a high number of independent processing units, enabling a high degree of parallelism. Exascale computing [9] refers to the ability of executing 10<sup>18</sup> floating-point operations within a second (FLOP/s). This is one of the most ambitious short-term challenges in high performance computing. Even though it has been reached under certain circumstances using distributed computing, by 2021 there are no listed supercomputers in the Top500 [125] reaching that performance. This order of FLOP/s would enable better accuracy in complex scientific applications and tasks such as weather forecasting [9], which relies on a vast amount of mutually dependent parameters; neural activity (The Human Brain Project [81]), which requires to simulate billions of interconnected neurons; personalized medicine, in order to classify pathologies based on medical history, current vital signs, etc.; some applications in fluid dynamics that would need more accurate solutions than current approximations for partial differential Navier-Stokes equations; and many others. As such, it is a critical milestone for computer engineering to reach.

For these reasons, the first objective of this Thesis is the exploration of the modern manycore architectures mentioned above. We target the Intel Xeon Phi x200 Knights Landing architecture, nowadays discontinued even though its high-level architectural legacy lives on the newer Intel Xeon Scalable generations. We focused on the performance of its mesh interconnection network, as this architecture was the first attempt by Intel to reach Exascale computing. The key idea beneath its design was to provide an efficient mesh of interconnected AVX-512-capable cores, organized in tiles, and equipped with a 3D-stacked high-bandwidth memory on-package. In theory, these features should allow highly parallel applications to fully

exploit memory bandwidth, and take advantage of large vector widths to improve the overall performance in terms of FLOPS/s. This architecture also presented a distributed directory for keeping coherence within the tiles and cores in the mesh in the form of a Cache/Home Agent (CHA). Memory addresses are distributed among slices of this distributed directory according to a non-disclosed hash function, i.e., each tile holds a set of the memory addresses in the system. Accesses to memory are supposed to present a UMA behavior, but, as we will detail later, after some experiments we discovered significant deviations on these memory latencies. With this knowledge we first built a model based on reverse engineering of the physical layout for developing an extension for the Tejas Simulator in order to model the behavior of the traffic in the interconnection network. Leveraging this information, we also developed static and dynamic techniques for improving the core-to-CHA affinities in the applications for reducing traffic contention and memory latencies in the network. Our findings and methodology employed are described in detail in Chapters 2 and 3.

With Knights Landing, Intel also introduced new instructions using up to 512bit width vectors with the AVX-512 instruction set. This new extension clearly stated the intention to exploit Instruction- and Memory-Level Parallelism (ILP and MLP, respectively) in high performance computing. Notwithstanding the potential benefits for memory bandwidth, AVX-512 presented some limitations in Knights Landing (and some subsequent generations) since it reduced drastically the CPU frequency [24, 26] when running certain instructions of this SIMD ISA. In addition, there are many variants of AVX-512, increasing the fragmentation in x86 architectures. Specifically, this fragmentation in the SIMD ISAs manifests the need of synthesizing ad hoc code for each platform. But these are not the only limitations: compilers according to their cost model could also decide not to use these vector capabilities, or even the very nature of the codes might not be suitable for those large vector widths without additional tuning. There are codes, such as Sparse Matrix-Vector Multiplication (SpMV), which are important kernels in machine and deep learning applications, presenting sparse and irregular accesses to memory (i.e., non-contiguous memory accesses). These access patterns prevent compilers, in most cases, to perform any type of vectorization in the code. Accordingly, the second objective of this Thesis is the development of SIMD optimizations by 1) proposing a novel approach for packing those random vector operands, and 2) fusing operations

such as independent reductions, also present in irregular codes such as SpMV. We propose an SMT-based system for automatically generate these packing candidates based on the instructions available in the ISA. With these candidates, we can generate a cost model for each platform according to the best candidate based on its performance. For automating the generation of these cost models we also developed a profiling and performance analysis toolkit, which is described in Chapter 4. This toolkit was conceived for building these costs models empirically, but it can be used for profiling any other kernel or application. All this toolchain leads to the source-to-source compiler we have implemented for synthesizing efficient platformaware SIMD code. This compiler is fully detailed in Chapter 5, including the SIMD optimizations described for the packing and fusion of operands and operations in a vector fashion. Finally, conclusions and future work of the Thesis are described in Chapter 6.

-Ken Thompson

2

# Effect of Distributed Directories and Optimization of Coherence Traffic in Manycores

#### Chapter's contents

| 2.1 Introduction                                      | 8  |

|-------------------------------------------------------|----|

| 2.2 Intel Knights Landing (KNL): Xeon Phi x200        | 10 |

| 2.3 Mapping the Knights Landing Processor             | 15 |

| 2.4 Processor Affinity and Data Layout                | 19 |

| 2.5 Experimental Results Varying Processor Affinities | 21 |

| 2.6 Reverse Engineering the CHA Mapping               | 27 |

| 2.7 Runtime Optimization                              | 34 |

| 2.8 Compile-time Optimization                         | 40 |

| 2.9 Discussion and Related Work                       | 50 |

|                                                       |    |

In this chapter we will review and study the most important aspects of modern manycore architectures, focusing on the Intel Knights Landing architecture and its distributed cache coherence directory, which play a key role in the optimization and scaling of modern manycore architectures. We also propose and assess optimizations for improving data locality by leveraging architectural details of the processor.

#### 2.1 Introduction

Computer architecture has evolved quickly in the past century, from very simple monolithic cores to thousands of interconnected processors in large clusters. Parallelism plays an important role in this evolution, as manycore architectures are one of the most promising candidates to reach the Exascale computing era. Manycore architectures are an evolution of classic multicore architectures which increase the number of interconnected cores. Coherence traffic was a limiting factor in classic multicore architectures, as scaling the number of cores on a cache coherent system caused a growth in the overhead associated with the cache coherence protocol, limiting the ability of a program to extract increased performance from the system. This was known as the "coherence wall" [70, 82]. Manycore architectures typically implement distributed cache directories to alleviate this limitation. This directory must be accessed each time a core requests access to a memory block which is not already locally available in the appropriate state (i.e., not invalid). This distributed design increases the scalability of the coherence system by removing the bottlenecks that a centralized directory would impose: the roundtrip from each core to the directory and the volume of requests that the directory would process. Intel implemented this distributed mechanism on its first manycore architecture Knights Landing [8]. This architecture organizes the processing units in a mesh of tiles, where each tile features two cores, a shared L2 cache, and a portion of the distributed directory named Caching/Home Agent (CHA). Each CHA holds a set of cache line addresses, which are distributed among all CHAs using a built-in address hash. As such, cache miss requests are bypassed directly out to the mesh to be serviced by a specific CHA as determined by the address hash. However, this CHA has also a cost, and quantifying the impact on performance is not trivial, as non-disclosed hash functions are used for distributing data, hardening any programmatically optimization. For these reasons, in this chapter we propose a reverse engineering process for obtaining those hash functions, an analysis of the effect of core affinity on memory latency, and different techniques for improving data locality on these architectures. More

specifically, in this chapter we describe the following contributions:

- We propose a mechanism to discover the physical layout of the logical components (cores and CHAs) of a mesh interconnect-based processor, as well as the mapping of memory blocks across CHAs and memory interfaces (Section 2.3).

- Leveraging the previous contribution, we analyze the impact of coherence traffic in the memory latency of distributed directory architectures. Mechanisms to optimize coherence traffic are proposed, improving core-to-CHA and threadto-core affinity (Section 2.4).

- We gather and analyze data generated by a large number of executions on a KNL unit, and develop optimized strategies for scheduling a set of tasks across the tiles in the mesh. We perform experiments to quantify the efectiveness of our optimizations. Our results reveal that exploiting the multiple opportunities for locality in a mesh interconnect is essential to increase the potential performance of future manycores (Section 2.5).

- With the information extracted in Section 2.3, the mapping of memory blocks to CHAs is reverse engineered. Binary functions which compute a target CHA from a physical memory address are exposed and shown to be pseudo-random in nature (Section 2.6).

- Different optimization strategies to improve memory latency by leveraging the mappings between memory and CHAs are designed. Approaches are proposed based on both dynamic and static work scheduling (Sections 2.7 and 2.8).

- Experiments are performed to quantify the effectiveness of the proposed optimizations. It is shown how the proposed schedulings improve memory latency by exploiting CHA proximity. However, due to the pseudo-random nature of the block-mapping functions the implementation of these schedulings affects other performance-impacting factors, which may ultimately lead to performance degradation (Sections 2.7.1 and 2.8.2).

The rest of the chapter is structured as follows: Section 2.2 delves deeper into manycore architectures and the Intel KNL. Section 2.3 presents the reverse engineering process to map logical components of an MI-based architecture to its physical layout. In Section 2.4 we describe the approach followed to optimize the coherence traffic. Section 2.5 evaluates the potential advantages of the proposed approach, and develops ways to exploit the architectural characteristics of a particular KNL unit. Section 2.6 details the reverse engineering process that leads to the discovery of the memory-to-CHA mapping. Sections 2.7 and 2.8 detail runtime- and compile-time-based approaches, respectively, to optimize coherence traffic, and summarize the results of the experimental evaluation phase. Finally, Section 2.9 discusses the results obtained, the viability of the approaches presented, and related work.

#### Intel Knights Landing (KNL): Xeon Phi x200

2.2

The increasing demand of computational resources over the last decade has shifted architectural paradigms. The relationship between energy consumption and frequency, known as Dennard's scaling, is not linear anymore [27]. The "multicore crisis" in the past decade was partially a response to this problem. The idea behind manycore processors is to comply with thermal limitations by integrating a higher number of simpler, slower processors, capable of taking advantage of embarrassingly parallel applications or to execute many smaller workloads at the same time. Even though cores are simpler, they can communicate more efficiently since they are integrated inside a single processor die and connected to a network-on-chip (NoC).

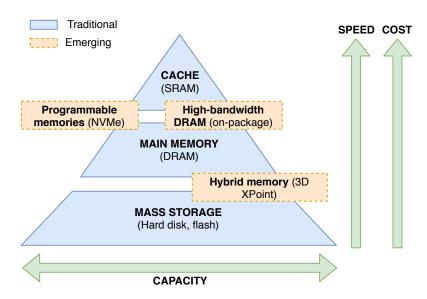

Manycore organizations present a challenge for the memory system. Since more data-hungry cores coexist now inside a single die, the memory wall grows higher. Modern architectures propose to use heterogeneous memory hierarchies, which combine different memory technologies with their own characteristics and trade-offs. Traditional memory hierarchies are augmented with these new technologies as shown in Figure 2.1, contributing to reduce the gap between processor and memory speeds.

This work focuses on the Intel Xeon Phi x200 architecture, codenamed Knights Landing (KNL), released in 2016 and discontinued in mid-2018. However, the distinguishing characteristics of its NoC live on the newer Intel developments for HPC, namely the Xeon Scalable processors, whose third generation codenamed Ice Lake was announced in 2020 [96]. Intel KNL is presented as a standalone x86 processor. In contrast, its predecessor, Knights Corner, was a co-processor which required

Figure 2.1: Traditional memory hierarchy updated with new emerging technologies.

a general purpose host processor. KNL is therefore not limited by the on-board memory size or the PCIe bus bandwidth. Moreover, the use of the x86 ISA enables KNL to execute different operating systems, legacy libraries, and general purpose applications. As such, KNL is more versatile than its predecessor and than current GPUs, which need applications to be rewritten following specific paradigms such as CUDA [65].

The rest of this section discusses the main characteristics of the Intel KNL: its internal organization, core architecture, on-die interconnect, memory system, and cluster and memory modes.

#### Internal organization 2.2.1

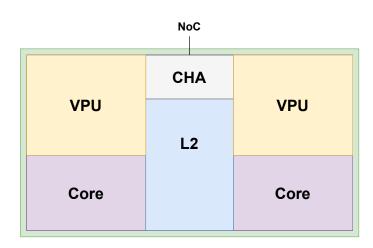

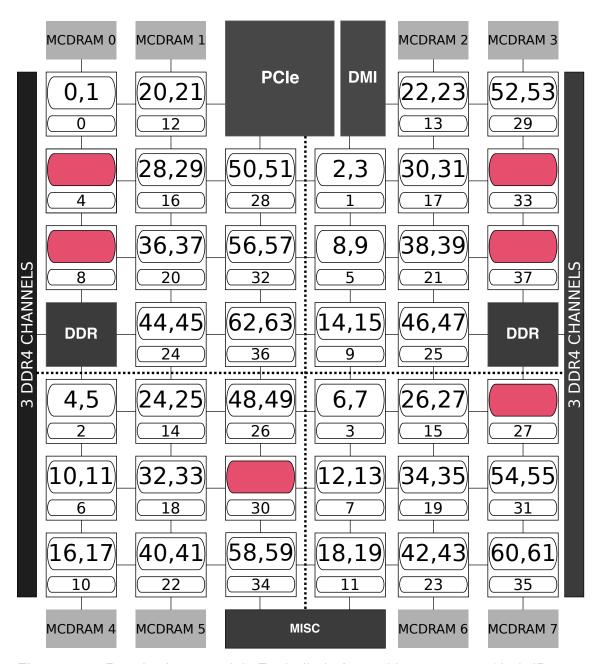

KNL integrates up to 72 cores organized in a 2D mesh of 38 tiles. Each tile comprises two cores, two vector processing units (VPUs), an L2 cache (shared between cores within the same tile, but private to the rest), and a portion of the distributed directory named Caching/Home Agent (CHA), as shown in Figure 2.2. Each CHA holds a set of cache line addresses, which are distributed among all tiles and their respective CHAs using a built-in address hash. In this way, cache miss requests are

Figure 2.2: High-level tile organization in KNL.

by passed directly out to the mesh to be serviced by a specific CHA as determined by the address hash. Depending on the particular processor model, the number of tiles enabled varies between 32, 34 and 36, featuring 64, 68 and 72 enabled cores, respectively. When a tile is disabled, the cores and caches within are also deactivated. However, the CHA and the logic for routing within the interconnection network remain active for all tiles, even those disabled. The CHA acts as the connection point between a tile and the mesh. While the CHA box physically resides in the tile, it is logically part of the on-die interconnect mesh.

Intel KNL cores are two-wide out-of-order derived from low-power Silvermont cores, designed for Intel Atom processors but modified to make them suitable for HPC [62]. They have been enhanced with AVX-512-capable VPUs. Furthermore, each core has a private 32-KiB L1 data cache, backed up by a 1-MiB L2 shared with the other core in the same tile but private to it. The CHA manages a portion of the distributed cache directory, which stores the status and location of the most up-to-date copy of a memory line, queried when an L2 miss occurs.

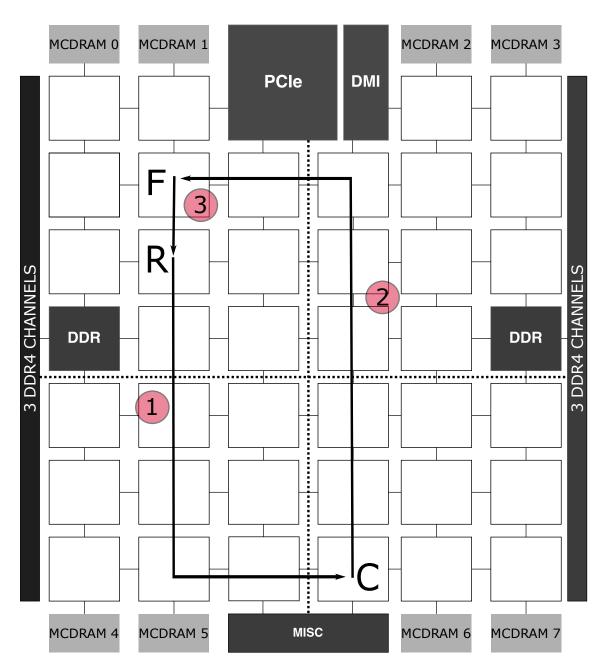

KNL features a 2D mesh NoC, replacing the ring topology used in Knights Corner, as depicted in Figure 2.3, which corresponds to the Intel Mesh Interconnect architecture. Messages traverse the mesh using a simple YX routing protocol: a transaction always travels vertically first, until it hits its target row. Then, it begins traveling horizontally until it reaches its destination. Each vertical hop takes 1 clock cycle, while horizontal hops take 2 cycles. The mesh features 4 parallel networks or

rings, each customized for carrying different types of packets [58]:

- AD ring (address ring): carries tile read/write requests and memory controller snoops to the CHA.

- BL ring (block ring): carries data transfers (two transfers for one cache line).

- AK ring (acknowledge ring): carries acknowledgements from memory controller to CHA and from CHA to tile. It also carries snoop responses from core to CHA.

- IV ring (invalidate ring): carries CHA snoop requests of tile caches (i.e., L2 cache misses).

#### 2.2.2 Memory system